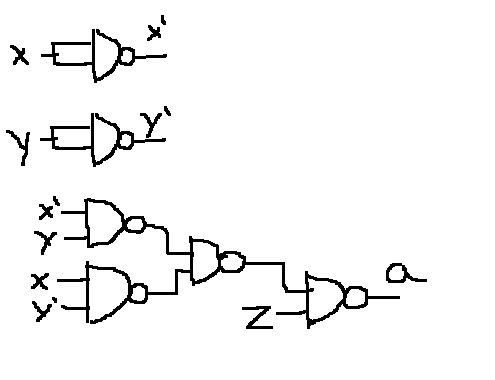

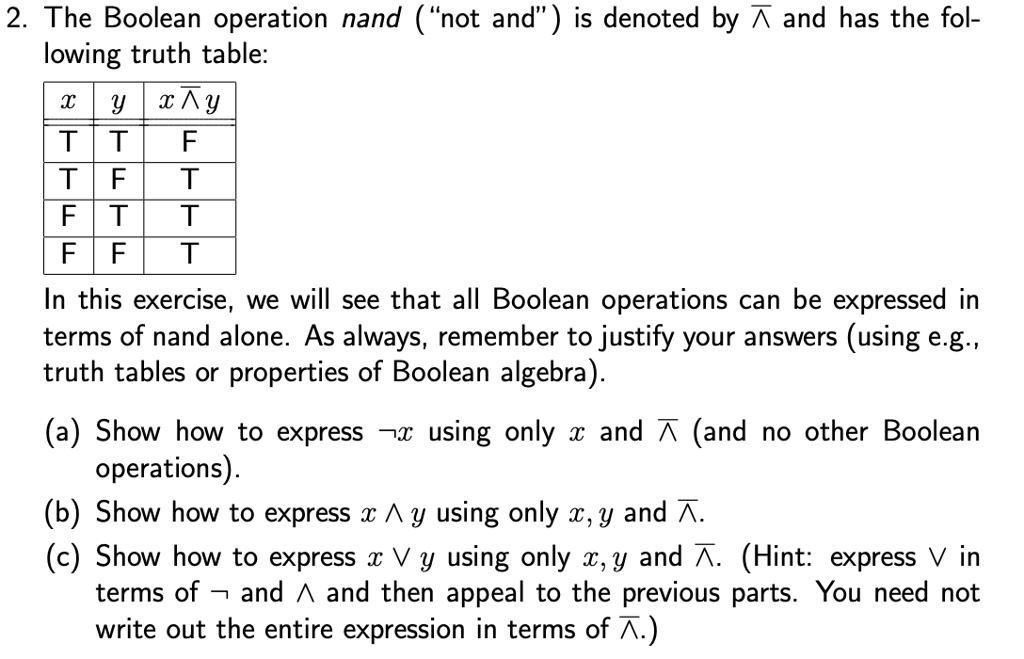

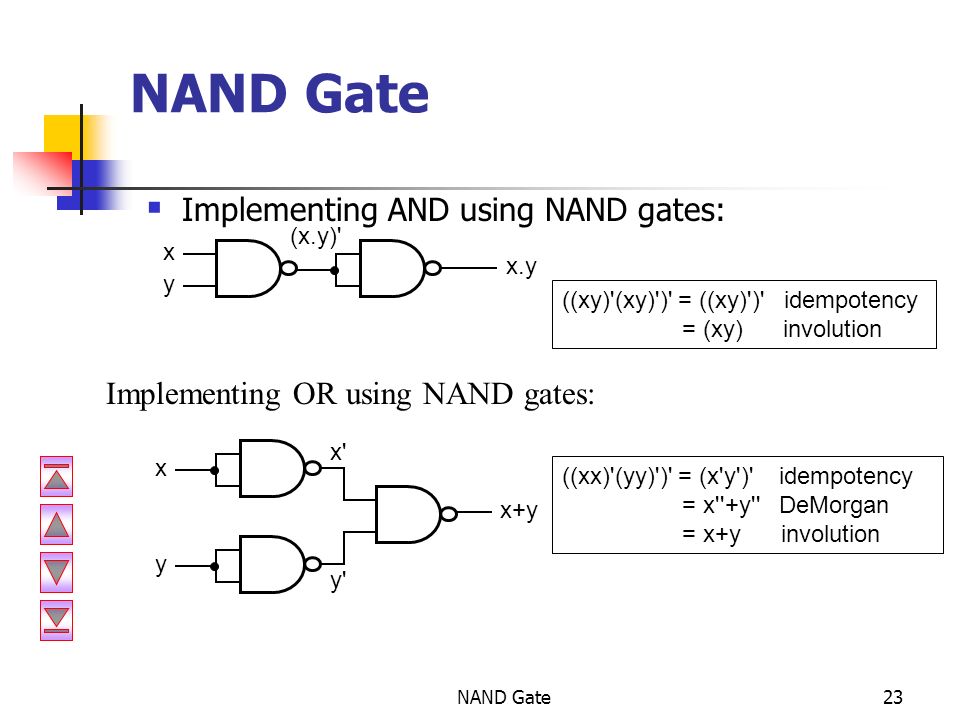

Is there something in particular youre having trouble with NANDs and NORs are universal so at worst you can just replace all gates with their NAND/NOR equivalent and be on your way. Your question is asking you to use NAND gates to compare things over and over until you you get a column of zeroes and ones that looks the same as X+Y does. NAND(NAND(x, y), NAND(NOT(x), NOT(y), NAND(NOT(Y), Z)) 2. That said, your last question doesn't make much sense. It actually stands for "not and." So if you ANDed two things together and got 0, then NANDing the same two things together would give you 1. If you have register pairs, you can load x in the low register of a pair and then shift left N-1 times for N bit wide registers. You didnt say anything about your processor. Now you could do X AND Y, X AND 1 or X AND (X OR Y) just by comparing the numbers in the first column with numbers in the second, third or fourth columns, respectively.Īs for NAND specifically, just remember that it means the opposite of AND. NAND operates bitwise, so the only hope you have of getting information between bit positions with an instruction is the carry in an add. All that matters is whether the value is a 0 or a 1, in the end. The thing you're comparing X with doesn't have to be called Y it can be any variable, any constant or the result of another comparison. In Chapter 8 we will see how these concepts can be used to construct the heart of a computer-the CPU.Yes, X NAND 1 is like X NAND Y with Y fixed as 1. h., wenn mindestens ein Eingang 0 ist, wird eine 1 ausgegeben. Ein NAND-Gatter gibt am Ausgang 0 aus, wenn alle Eingänge 1 sind. The example above shows that two solutions that look the same on paper may be dissimilar in hardware. Ein NAND-Gatter (von englisch: not and nicht und) ist ein Logikgatter mit zwei oder mehr Eingängen A, B, und einem Ausgang Y, zwischen denen die logische Verknüpfung NICHT UND besteht. Since there usually is not a unique solution, you often need to develop several designs and analyze each one within the context of the available hardware. The conversion from an AND/OR/NOT gate design to one that uses only NAND gates is straightforward:Ĭonvert the products (AND terms) and the final sum (OR) to NANDs.Īdd a NAND gate for any product with only a single literal.Īs with software, hardware design is an iterative process.

Thus, the NAND gate implementation is a less expensive and faster implementation. But we saw in Section 6.2 that a NAND gate requires fewer transistors than an AND gate or OR gate due to the signal inversion properties of transistors. This provides a high-speed, low-cost solution for 5G, AI, and many applications. It can provide 3 times faster speed and more than 10 times of data throughput than the conventional NAND flash, without increasing any cost or footprint. A X NAND Y NAND Z Z C NAND Draw a truth table for this circuit. Question: Consider the following logic circuit. If a set of inputs would result in the outputs constantly changing (an unstable state), put 'error' as the output. The function in Equation (6.3.5) using only three NAND gates.įrom simply viewing the logic circuit diagrams, it may seem that we have not gained anything in this circuit transformation. X-NAND is a revolutionary 3D NAND flash memory architecture. A X NAND Y NAND Z Z C NAND Draw a truth table for this circuit.

X NAND Y NAND X NAND Y FULL

100 (1 rating) If you have any query then ment View the full answer.

We review their content and use your feedback to keep the quality high. Who are the experts Experts are tested by Chegg as specialists in their subject area. Show transcribed image text Expert Answer. NANDĪ binary operator the result is \(\binary\)įigure 6.3.9. Nand (x + y) Nand(not(xy) + not(yz)) Nand (y + z) let me know if you can help me out a bit with the output. And, of course, the same is true for OR gates, giving us a NOR gate. The combination is so common, it has been given the name NAND gate. We saw in that discussion that it takes fewer transistors to produce AND NOT than a pure AND. As a result, an AND gate typically requires a NOT gate at the output in order to achieve a true AND operation.

That is, a high voltage at the input produces a low voltage at the output and vice versa. Because of the inherent way that transistors work, most circuits invert the signal. The discussion of transistor circuits in Section 6.2 illustrates a common characteristic.

In the previous tutorial, we looked at AND gates, OR gates and signals in VHDL.This tutorial covers the remaining gates, namely NAND, NOR, XOR and XNOR gates in VHDL.